单片机内部的ADC通常是单端采样的,根据型号和配置的不同,可能存在0~ 3V和0~ 3.3V等不同配置。但对于交流系统,我们采样的原始信号往往是双极性信号,例如交流电压 +/- 220V。这些信号往往不在单片机ADC的单极性采样范围内,所以需要通过运算放大器电路对信号进行缩放和平移,使得一个大范围的双极性信号变成一个适当范围的单极性信号。

经典电路:同相放大器+1.65V偏置电路

以0-3.3V的采样电路为例,上述信号变换可以视为把交流信号变换到-1.65V~ 1.65V范围内的交流信号,然后再叠加1.65V的偏置。

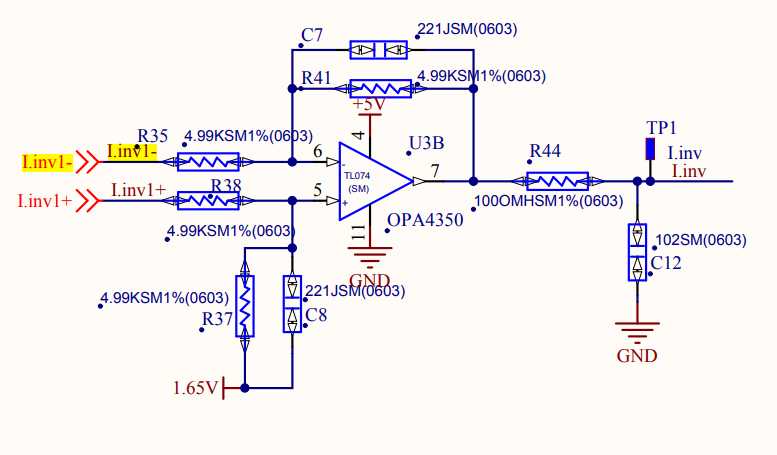

上图是从TI的参考设计HV_SOLAR_DC_AC_v1.1中摘出的。

我们利用运算放大器的虚短虚断,先忽略电容C7,C8,可以得到如下公式

v_{0}\frac{R_{35}}{R_{41}+R_{35}}+v_{-}\frac{R_{41}}{R_{41}+R_{35}}=v_{+}\frac{R_{37}}{R_{37}+R_{38}}+1.65\frac{R_{38}}{R_{37}+R_{38}}

=>

v_{0}=(v_{+}-v_{-})+1.65

此电路假设v_{+}-v_{-}在(-1.65~ 1.65V)之间,则输出信号幅值在(0~ 3.3V)之间。

现在我们考虑电容并分析完整的电路频域特性。首先这些电阻都是4.99K,所以我们用R来代替。R41和C7并联,R37和C8并联,并联后的线路阻抗记为Z

Z = R/(1+RCs)

这里1/(1+RCs)是一个低通滤波器f_{l1},截至频率为\frac{1}{2\pi RC}Hz,这里计算可得L1的截至频率约为15kHz。

利用虚断虚短,我们可以得到

(v_0-1.65) = (v_+ – v_-)Z/R = (v_+ – v_-)f_{l1}

这个运算电路输出又级联了一个RC低通滤波器f_{l2},其截至频率为160kHz。

至此,我们得到了这个经典的1.65V偏置叠加电路的运算规则和滤波特性。

若进一步将这个电路中的R35/R41和R38/R37的比值记为x,

则电路模型为

(v_0-1.65) = (v_+ – v_-)Z/(Rx) = (v_+ – v_-)f_{l1}/x

通过配置x,可以实现对输入信号(v_+ – v_-)的缩放。

经典问题:1.65V怎么来的

通常情况下开发板上是没有直接外接1.65V的,有两类方式可以获得1.65V。

第一类方式就是利用1.65V电源基准芯片获得1.65V。这种方法设计看似简单,但成本较高,另外要注意通常高精度的电源基准芯片的负载能力有效,即不能输出多少mA的电流,在上一节中其实我们注意到1.65V会通过电阻R37消耗一定的电流,当采样电路通道较多时,这个电流会消耗多少,会不会超出电源基准芯片的负载能力需要进行核验。

第二类方式就是利用电阻分压,从3.3V中获得1.65V电压。

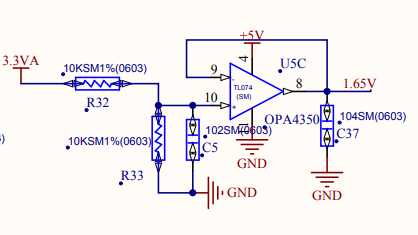

上图同样是从TI的参考设计HV_SOLAR_DC_AC_v1.1中摘出的。

我们可以看到R32,R33均为10k的电阻,分压产生了1.65V,这个1.65V再经过一个电压跟随器产生最终送往各运放支路的1.65V。这里第一个电容C5和R33组成了160KHz低通滤波,C37是0.1uF的电容,提供一定的稳压作用,此电容不宜取得太大,防止产生稳定性问题,可以回顾LDO输出电路设计。

这里为什么要加一个电压跟随器呢,主要是起到一个阻抗变换的效果。由于1.65V是分压得到的,当1.65V被送往其它运算电路时它还会和一堆电阻产生运算关系,这些运算关系要求1.65V可以被视为一个没有串联内阻的理想电压源。显然直接通过R32和R33两个电阻是无法实现这一点的。

ADC限幅保护

有些时候采样信号的可能电压范围范围和额定电压范围有着明显的区别。比如一个电机的额定电流是10A,但是它也可能发生短路瞬间达到100A。我们显然不希望将ADC的范围和+/- 100A对应,因为这样会导致通常情况下的额定10A电流无法获得高精度的采样。所以我们会根据额定电流大小设计采样电路运算放大器的运算规则,然后利用钳位电路实现对ADC的保护。

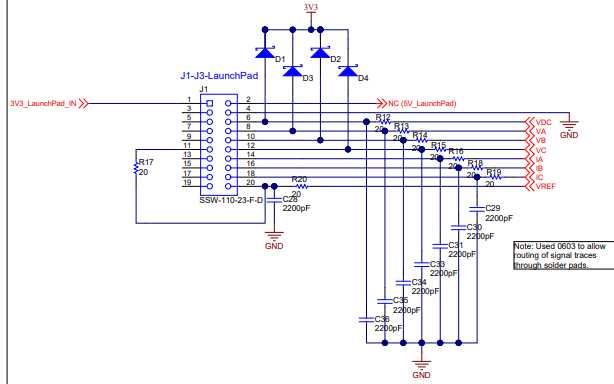

上图是从TIDROK2.PDF中摘出的钳位电路,当输出信号过大时,肖特基二极管D1-D4被导通,电压被钳位在3.3V+D1-D4的导通压降。对于交流信号,为了防止ADC端口出现严重的负电压,可以在信号和GND直接接入类似的钳位二极管。为了更好的保护ADC,例如满足下图中的要求(TI-F28379d),此处D1-D4的导通压降应较小,为0.3V。

练习

为F28379DLaunchpad的ADC设计运放电路,使得它能接受+/-10V范围内的采样信号,并且提供最大3.3V的限幅保护。